Thus with M = 1 the circuit works as a down counter. These connections will produce a down counter. Hence Q A bar gets connected to the clock input of FF-B and Q B bar gets connected to the clock input of FF-C. are enabled whereas the AND gates 1 and 3 are disabled. Thus with M = 0 the circuit work as an up counter. These connections are same as those for the normal up counter. Hence Q A gets connected to the clock input of FF-B and Q B gets connected to the clock input of FF-C. will be enabled whereas the AND gates 2 and 4 will be disabled. If M = 0 and M bar = 1, then the AND gates 1 and 3 in fig. Let the selection of Q and Q bar output of the preceding FF be controlled by the mode control input M such that, If M = 0, UP counting. UP/DOWN − So a mode control input is essential.įor a ripple up counter, the Q output of preceding FF is connected to the clock input of the next one.įor a ripple down counter, the Q bar output of preceding FF is connected to the clock input of the next one. This will operate the counter in the counting mode. For this mode, the mode select input M is at logic 0 (M=0).ĭOWN counting mode (M=1) − If M = 1, then the Q bar output of the preceding FF is connected to the next FF. UP counting mode (M=0) − The Q output of the preceding FF is connected to the clock of the next stage if up counting is to be achieved. But the clock to every other FF is obtained from (Q = Q bar) output of the previous FF. The LSB flip-flop receives clock directly. So either T flip-flops or JK flip-flops are to be used. In the UP/DOWN ripple counter all the FFs operate in the toggle mode. A combinational circuit is required to be designed and used between each pair of flip-flop in order to achieve the up/down operation. A mode control (M) input is also provided to select either up or down mode. Up counter and down counter is combined together to obtain an UP/DOWN counter. On application of the next clock pulse, Q A will change from 1 to 0 as Q B will also change from 1 to 0.ĭepending on the way in which the counting progresses, the synchronous or asynchronous counters are classified as follows −

On application of the third falling clock edge, FF-A will toggle from 0 to 1 but there is no change of state for FF-B. On the arrival of second negative clock edge, FF-A toggles again and Q A changes from 1 to 0.īut at this instant Q A was 1. Logical Diagram OperationĪs soon as the first negative clock edge is applied, FF-A will toggle and Q A will change from 0 to 1.īut at the instant of application of negative clock edge, Q A, J B = K B = 0. The J B and K B inputs are connected to Q A. The J A and K A inputs of FF-A are tied to logic 1. If the "clock" pulses are applied to all the flip-flops in a counter simultaneously, then such a counter is called as synchronous counter. Q BQ A = 00 after the fourth clock pulse. Hence it toggles to change Q B from 1 to 0. This negative change in Q A acts as clock pulse for FF-B. On the arrival of 4th negative clock edge, FF-A toggles again and Q A becomes 1 from 0. So Q B does not change and continues to be equal to 1. Since this is a positive going change, FF-B does not respond to it and remains inactive.

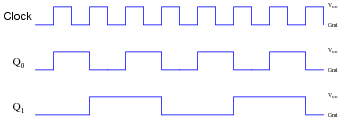

On the arrival of 3rd negative clock edge, FF-A toggles again and Q A become 1 from 0. Q BQ A = 10 after the second clock pulse. So it will also toggle, and Q B will be 1. The change in Q A acts as a negative clock edge for FF-B. On the arrival of second negative clock edge, FF-A toggles again and Q A = 0. There is no change in Q B because FF-B is a negative edge triggered FF. Since Q A has changed from 0 to 1, it is treated as the positive clock edge by FF-B. In timing diagram Q 0 is changing as soon as the negative edge of clock pulse is encountered, Q1 is changing when negative edge of Q 0 is encountered(because Q 0 is like clock pulse for second flip flop) and so on.Initially let both the FFs be in the reset stateĪs soon as the first negative clock edge is applied, FF-A will toggle and Q A will be equal to 1.

Every time Q 1 goes from 1 to 0, it complements Q 2, and so on. Every time Q 0 goes from 1 to 0, it complements Q 1. The lowest-order bit Q 0 must beĬomplemented with each count pulse. Or when the output to which it is connected goesįrom 1 to 0. In the CP input indicates that the flip-flopĬomplements during a negative-going transition All J and K inputs are equal to 1.įig: 4-bit ripple counter using JK Flip Flop The diagram of a 4-bit binary rippleĬounter is shown in Fig. Holding the least significant bit receives the incoming count pulses. The output of each flip-flop connected to the Clock Pulse input of the next higher-order flip-flop. Explain the 4 bit ripple counter and also draw a timing diagram.ġ0 Mark question | Asked in (TU CSIT) Digital LogicĪ binary ripple counter consists of a series connection of complementing flip-flops (T or JK type), with

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed